A Brief Plunify Simulation Tutorial

The following step-by-step guide to simulation is aimed at users new to Plunify or to FPGA design in general.

After a design is described in Verilog / VHDL, usually the next step is to run a simulation in order to verify if the general functionality is correct. There are many types of simulations and simulators.

Plunify can be used to simulate a Verilog / VHDL design, using the Icarus Verilog and GHDL simulators. The following example uses a simple counter in Verilog, provided by default when you register with us.

|

|

|

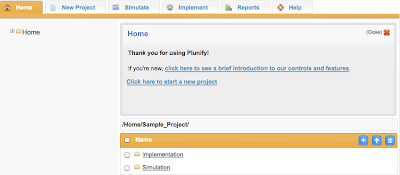

First, log on at www.plunify.com. The Project Manager's initial page appears. Your home directory and its contents are displayed on the left. Click |

|

|

|

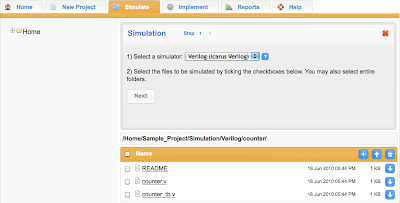

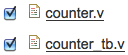

Click the "Simulate" tab. Select "Verilog (Icarus Verilog) as your simulator. Select your Verilog source files using the built-in file explorer. Click "Next". |

|

|

|

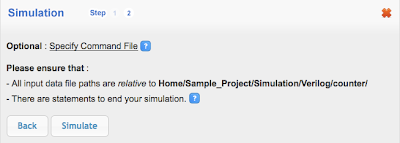

Click the "Simulate" button. (In this case, we don't have to specify a "Commandfile", which is a batch file that Icarus Verilog uses.) |

|

|

|

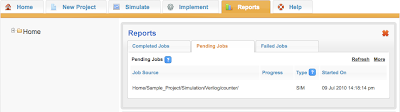

At this point, your simulation has started. Click "Close", followed by the "Reports" tab. Your simulation will be displayed under "Pending Jobs". |

|

|

|

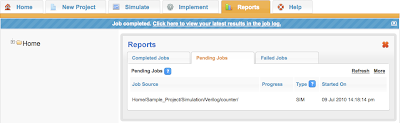

When the simulation completes, its job entry vanishes from "Pending Jobs" and appear in "Completed Jobs". A blue notification message also pops out near the top. To view results, click the above message (You will also be sent a notification email). |

|

|

|

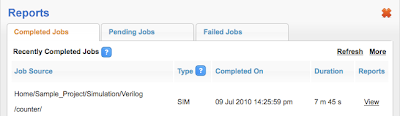

Click "View" beside your job entry in "Completed Jobs" |

|

|

|

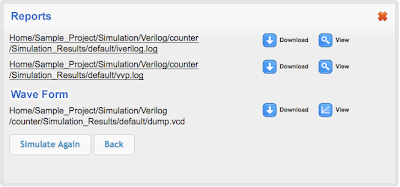

Two, potentially three types of results exist:

Click "View" beside each result to examine them. These files can also be downloaded. |

|

|

|

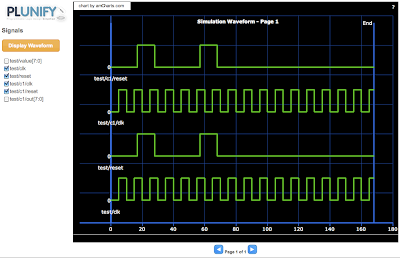

To view a simulation waveform, click |

|

|

|

Display relevant signals by selecting them and clicking the "Display Waveform" button. Use the scroll and zoom buttons to examine your waveform and debug your simulation. |

|

|

|

But of course, simulation is a repetitive process, at least until your design works. Make changes to your source files and upload them. Run the simulation again via the above steps, or use the |

This concludes our brief simulation tutorial.

Feel free to try the other examples as well, which include the same Verilog counter but with an Icarus Verilog command file, and a VHDL adder example that uses the GHDL simulator.

Questions / comments / kudos / hate mail can be sent to tellus@plunify.com