There are prudent reasons for not using too much of the FPGA's resources, because one almost always has to insert more logic to fix a failing timing path or a functionality bug. Even back in college, the digital systems professor made it a rule that we could only use up to 70% of the logic resources for our senior year capstone project (or get an 'F'). This 70% threshold is, of course, different depending on the device family and the design. There are customers who skilfully max out 100% of the logic resources.

Sometimes you just have to cram that extra logic (fix or feature) into the FPGA so that your products beats the competition's. On the practical side of things, maybe your company gets a bulk discount on a particular FPGA device and hence it makes sense for different product-lines to target the same device. Whatever the case is, to complement good design, modern FPGA tools provide numerous knobs to squeeze better timing and area performance out of your design. The right combination of these knobs can mean the difference between a snugly-fitted, optimised design and one that screams "Error: The design requires N memory bits but this device only has M." where M is some number smaller than N.

In the quest for performance and feature set fulfilment, testing the limits of synthesis and implementation is an invaluable way of recognising potential bottlenecks in and getting optimal performance from your design. As you may know by now, InTime is a tool that intelligently adjusts synthesis and place-and-route options to close timing and to help your design fit into the target device. What you may not have heard is that in cases where optimising for better performance sends the resource utilisation over the edge, InTime will react automatically and use area-saving options to reduce your design's resource usage.

The following example shows what happens:

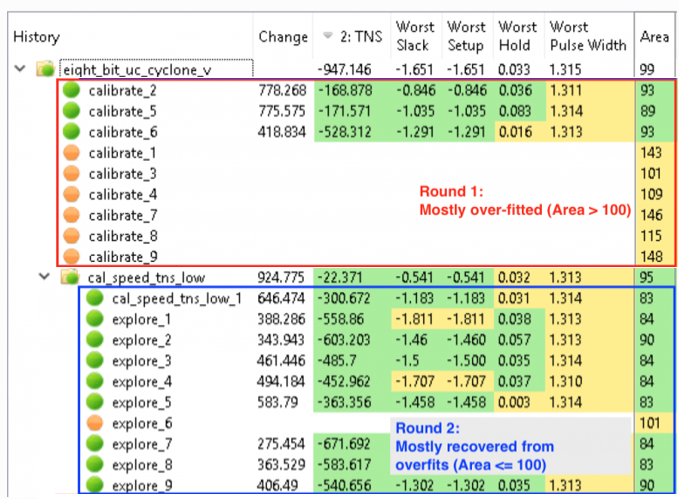

InTime results: 2nd round recovers from 1st round overfits.

As shown in the screenshot above, in round 1 (outlined in red), most of the results did not fit in the device. InTime detected this and adjusts the settings for round 2 (outlined in blue).

See: http://support.plunify.com/en/knowledgebase/how-to-set-overfitting-preferences/ for detailed steps.

There are many tools in an FPGA designer's toolkit. When InTime explores different optimisations, some results may over-fit, but you can let InTime adjust parameters by itself to rein in resource utilisation. Who knows -- you might yet be able to squeeze in that coveted feature.

Have a try and see for yourself. We'd love feedback on whether this new feature is useful or not!