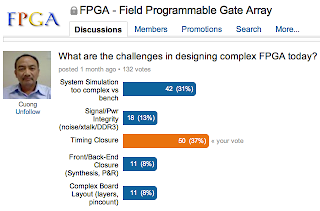

A poll on the challenges associated with FPGA design in an FPGA discussion group on LinkedIn caught my attention recently. Conducted by Cuong Nguyen from EDA Direct, it drew several lengthy comments.

|

| Poll: FPGA Design Challenges |

My vote went to Timing Closure - definitely one of the most frustrating and time-consuming classes of problems for me. Unlike functional bugs, timing problems can be rather unpredictable because there are more dependencies on the rest of the system, and also because different synthesis and place-and-route tools have their own unique options that can improve / worsen timing scores unexpectedly. This seems especially true when a design exceeds ~75% utilization and above. Which reminds me of a restriction placed on the FPGA team at a user's company where, at the code development phase, no design was allowed to exceed 70% total utilization.

The closer it gets to the deadline, the more urgent it is for the designer to find a timing solution without changing too much of the design. Upstream changes are rarely welcomed so if a tool option can result in positive slack, that would be very much preferred.

One rather brute-force approach that I've used before was to run a design against almost every conceivable tool option and just select the best results. Of course, that's assuming one has sufficient licenses, enough servers and suitable scripting experience, otherwise it is going to be very time- and resource-consuming. Over time, we've figured out a more optimized set of options that perform well for different designs, and are now pairing those with cloud computing resources to get a good blend of options vs tools+hardware. This approach has been working very well so far and we're improving it as we get more designs.

What's the most challenging thing that you've faced in FPGA design?

- harnhua